Michael Jørgensen

Michael Jørgensen

When we write a new assembler it would be nice if it supported macro instructions, i.e. defining a macro consisting of small snippets of assembly. Something similar to the 6502...

Oh, I didn't know about VASM. Thank you for the hint.

One more thing. On the hardware, this test should also verify that the signal `WAIT_FOR_DATA` doesn't create spurious accesses, i.e. that the read and write counts are unaffected. Are there...

I've started development on this on the separate branch `dev-cpu-bus-test`. It works in the simulator, but something fails in the hardware. I have not debugged that yet. The CPU Bus...

Not sure if this is a bug or not. I've started debugging the CPU Bus Test (CBT) on the hardware, and it fails on the first instruction: `CMP R0, @R2`....

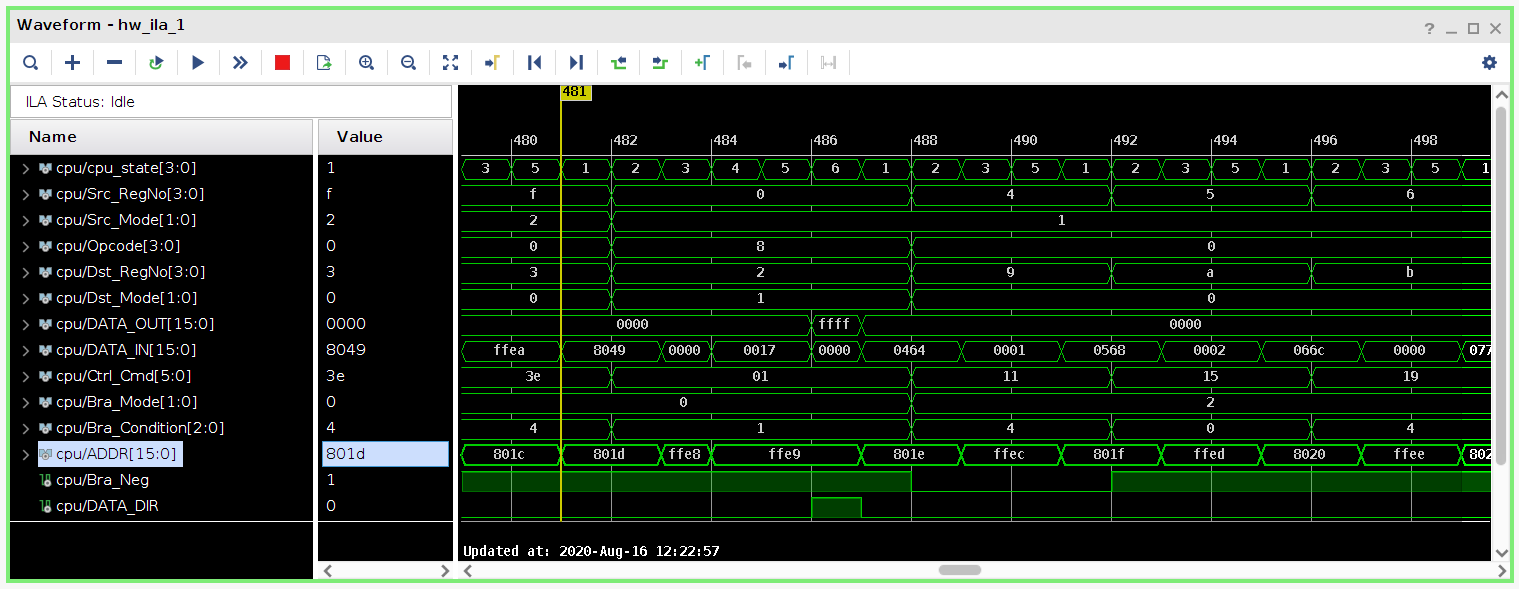

Here's another screen shot with a different instruction:  This shows the execution of the instruction `NOT @R0, @R2` (0x8049), where R0 = 0xFFE8 and R2 =...

I don't want to divert this discussion too much, but I have two comments: 1. You mention `WAIT_FOR_DATA`. With the changes to the tristate handling, the RAM no longer asserts...

Here is another SID implementation (in verilog): https://github.com/thomask77/verilog-sid-mos6581

There is already a working 6502 processor here: https://github.com/MJoergen/65c02 (made by me!). That implementation is not quite cycle exact, but could be made so, if the need is there.

Memory is a tough issue and a scarce resource. If we go for full bitmap graphics with 4 bits per pixel (16 colors), then that requires 1280x1024x4 / 16 =...