Baungarten-CINVESTAV

Baungarten-CINVESTAV

Sorry, I forgot to add this information. Those testbench was run with the task [preconfigured_testbench_without_self_checking](https://github.com/Baungarten-CINVESTAV/OpenFPGA_addr_test/tree/master/tasks/basic_tests/preconfig_testbench/preconfigured_testbench_without_self_checking/config)

Hello @tangxifan With the post-synthesis netlists from Yosys file are you talking about [xxx_ace_out.blif](https://github.com/Baungarten-CINVESTAV/OpenFPGA_addr_test/blob/master/tasks/basic_tests/preconfig_testbench/preconfigured_testbench_without_self_checking/run001/k6_frac_N10_tileable_40nm/adder_128_with_vector/MIN_ROUTE_CHAN_WIDTH/adder_128_with_vector_ace_out.blif),[ xxx_yosys_out.blif](https://github.com/Baungarten-CINVESTAV/OpenFPGA_addr_test/blob/master/tasks/basic_tests/preconfig_testbench/preconfigured_testbench_without_self_checking/run001/k6_frac_N10_tileable_40nm/adder_128_with_vector/MIN_ROUTE_CHAN_WIDTH/adder_128_with_vector_yosys_out.blif), [xxx.blif](https://github.com/Baungarten-CINVESTAV/OpenFPGA_addr_test/blob/master/tasks/basic_tests/preconfig_testbench/preconfigured_testbench_without_self_checking/run001/k6_frac_N10_tileable_40nm/adder_128_with_vector/MIN_ROUTE_CHAN_WIDTH/adder_128_with_vector.blif) , [xxx.net](https://github.com/Baungarten-CINVESTAV/OpenFPGA_addr_test/blob/master/tasks/basic_tests/preconfig_testbench/preconfigured_testbench_without_self_checking/run001/k6_frac_N10_tileable_40nm/adder_128_with_vector/MIN_ROUTE_CHAN_WIDTH/adder_128_with_vector.net) or [fabric_netlist.v](https://github.com/Baungarten-CINVESTAV/OpenFPGA_addr_test/blob/master/tasks/basic_tests/preconfig_testbench/preconfigured_testbench_without_self_checking/run001/k6_frac_N10_tileable_40nm/adder_128_with_vector/MIN_ROUTE_CHAN_WIDTH/SRC/fabric_netlists.v) file?

> @Baungarten-CINVESTAV Can you check if the post-synthesis netlists from Yosys is correct or not? This will help us to spot the bug. Hello, I have checked all the .blif...

This issues was solve in #880, Summary, icarous verilog has some flaws.

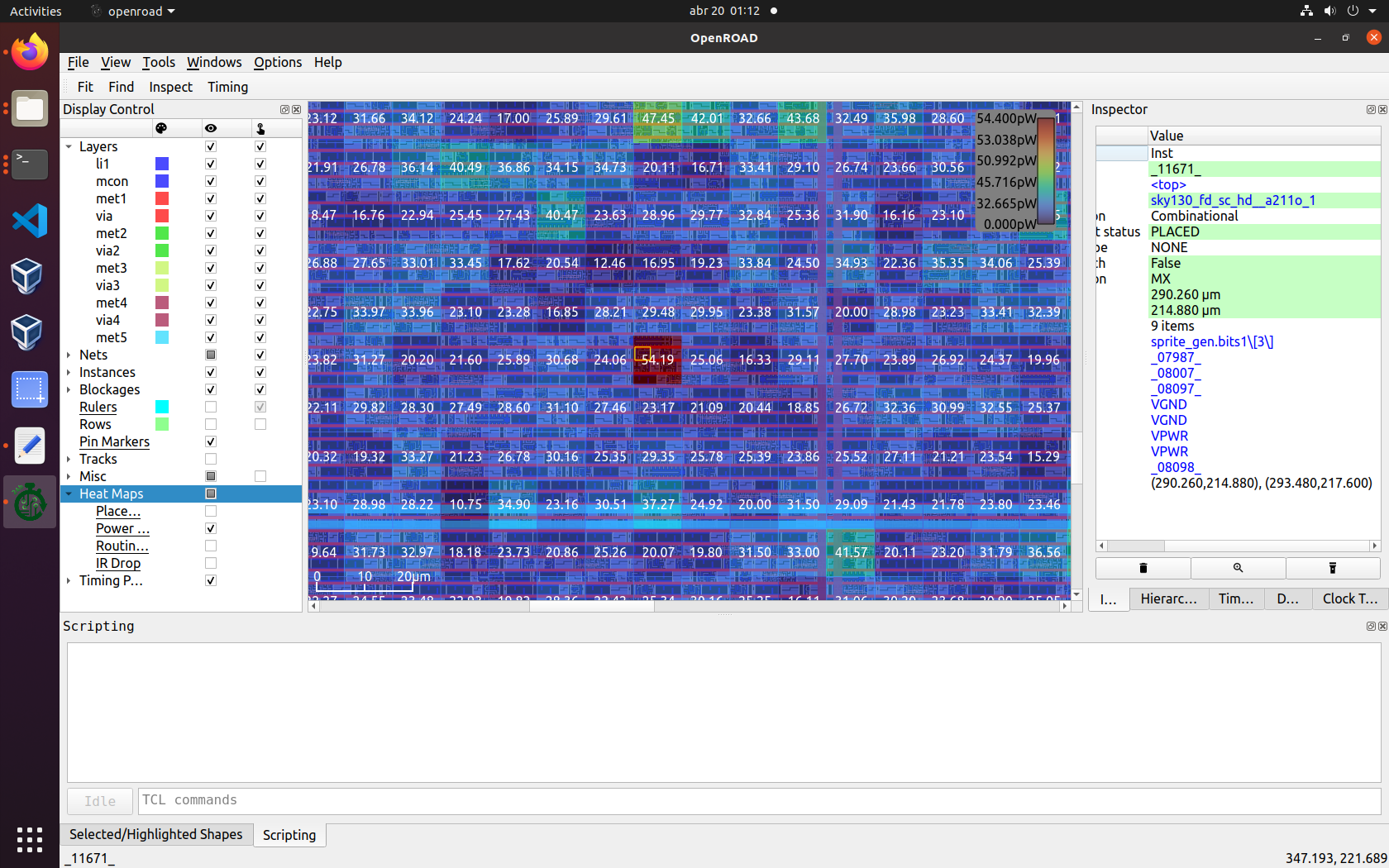

Hello, Could you help me with these questions? - What did you do to generate these images? - I mean, how can I see image like that of my own...

I compared the constraints of the previous version and the newest version and I noticed that the newest version didn't add automatically the constraint "MAX_TRANSITION_CONSTRAINT", the previous version added "MAX_TRANSITION_CONSTRAINT"...

If I remember correctly I solved the error by removing the "EXTRA_LIBS", this is used for time analysis and the OpenLane documentation indicates that it is optional.

@vijayank88 and @maliberty thanks for your quick answer. I'm running the OpenLANE flow with Caravel, and then i export the ".def" and ".lef" file in to "OpenROAD-flow-scripts". With your answers...

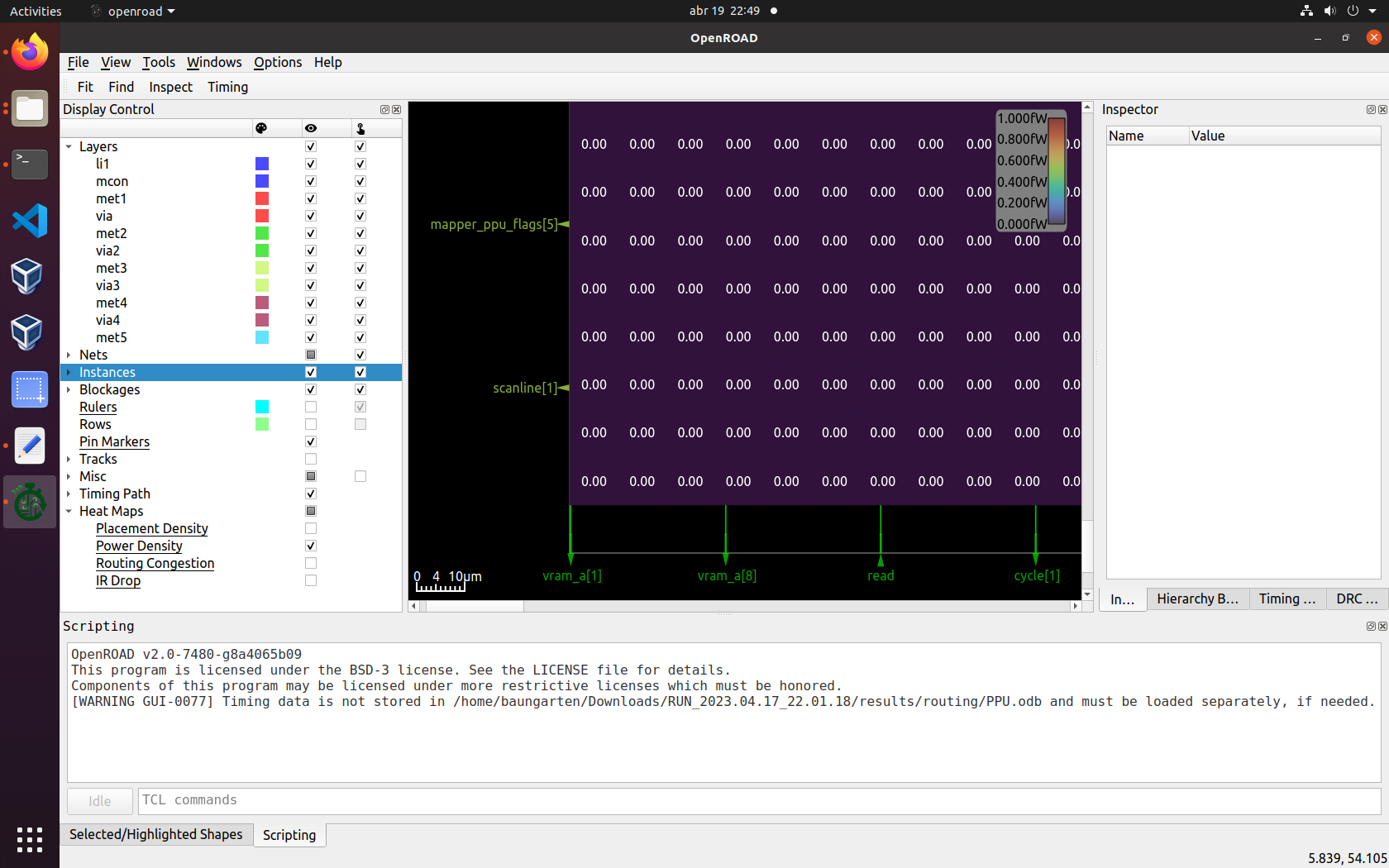

I installed the newest version of OpenROAD & OpenLANE, then i ran the PPU OpenLANE example, and finally i exported opened the ".odb" with OpenROAD -GUI...

Thanks, it works for OpenLANE direct workflow.  Maybe this is not the right issues but do you know why when I load a ".odb" file from...