Testbench gives multiples 1'bx when use high number of inputs/outputs

Hello every one,

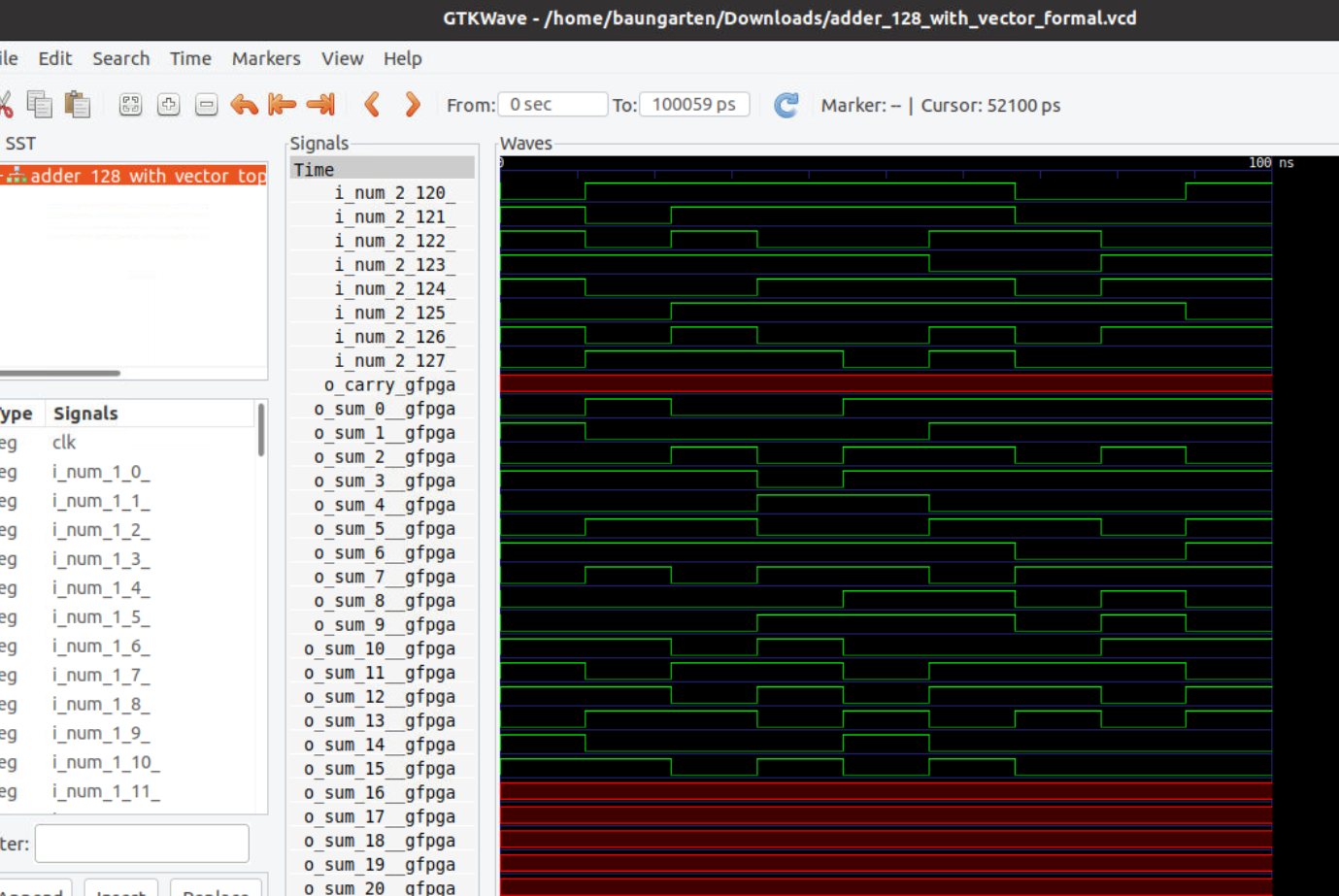

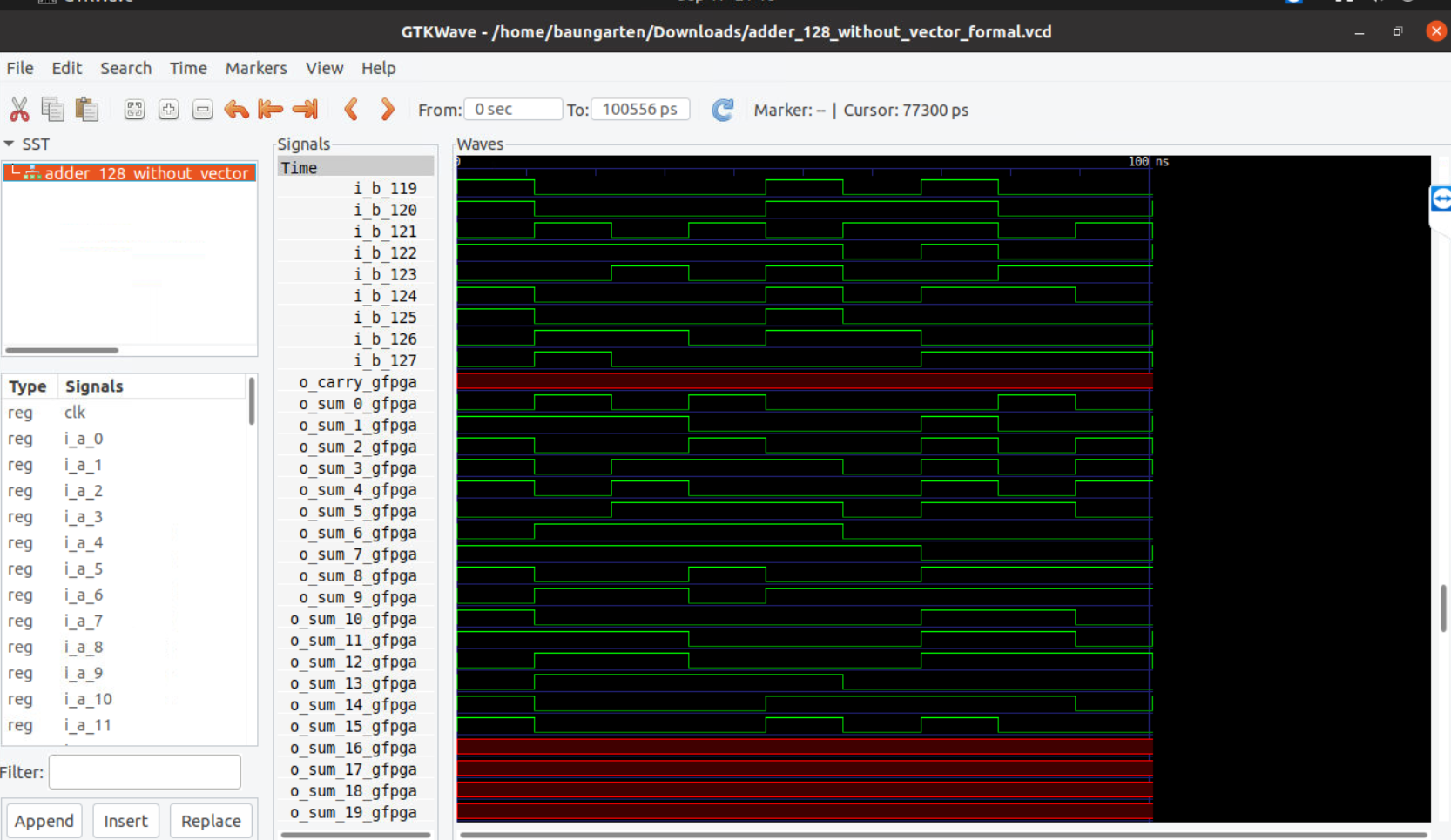

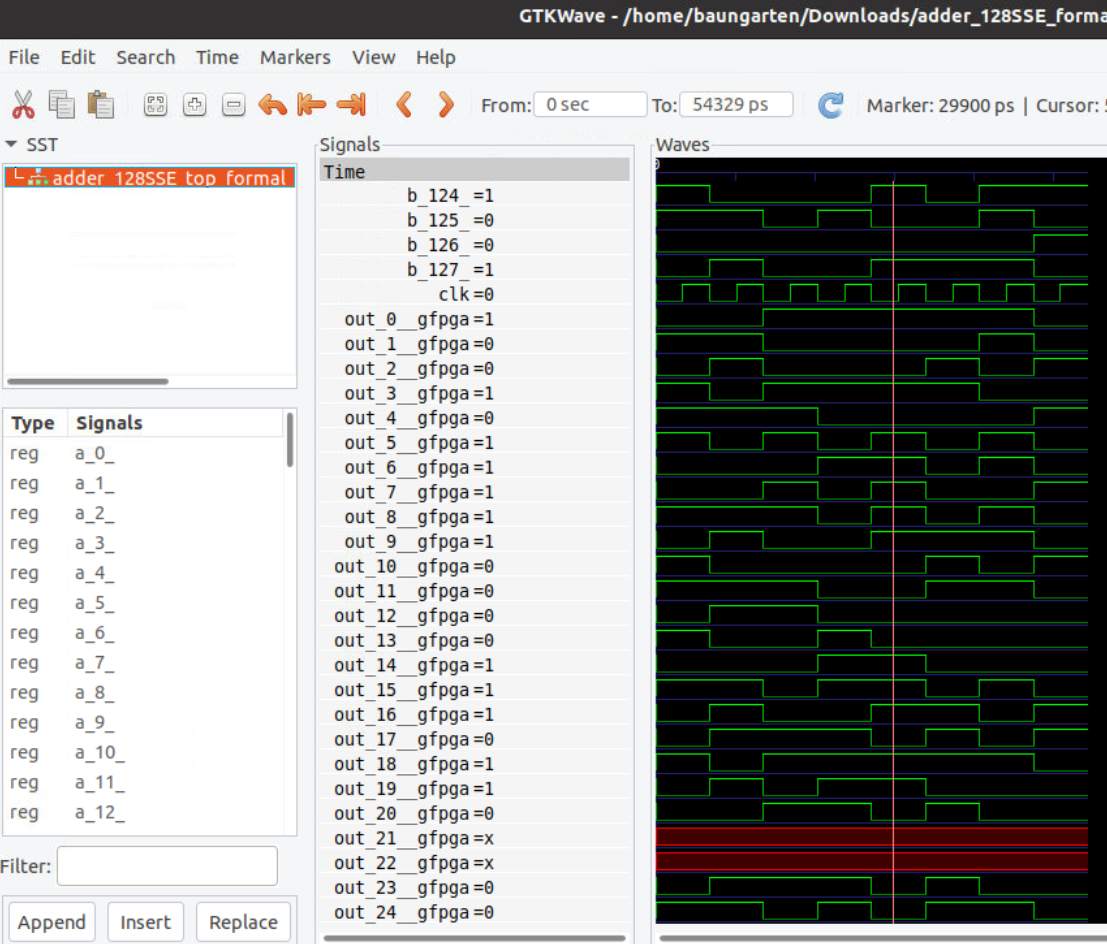

As the title says i had a couple of erros when i used mutiples i/o. Trying to find the mistake, i simplified my modules on a couple of adders:

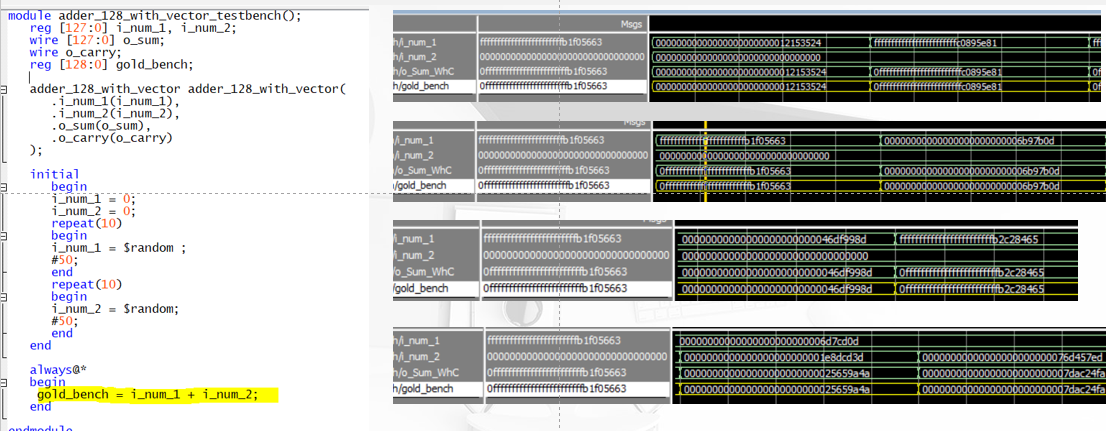

The module adder_128_with_vector is a simple add of two numbers of 128 bits, the output has 129 bits and the i/o are defined as a unitary vector, e.g. input [127:0] i_num_1.

The module adder_128_without_vector is a simple add of two numbers of 128 bits, the output has 129 bits and each i/o are defined 1 by 1, I thought the problem might be the definition of i/o.

the module adder_128SSE perform 4 adds of two numbres of 32 bits but it received just 1 input of 128 bits.

It can be seen in the previous images that each of the above testbenches has an error or unknow value.

I want to know what is wrong in my project and how i can solve my problem?

share my openfpga_flow folder

https://github.com/Baungarten-CINVESTAV/OpenFPGA_addr_test

Thanks in advance

Sorry, I forgot to add this information. Those testbench was run with the task preconfigured_testbench_without_self_checking

@Baungarten-CINVESTAV Can you check if the post-synthesis netlists from Yosys is correct or not? This will help us to spot the bug.

Hello @tangxifan

With the post-synthesis netlists from Yosys file are you talking about xxx_ace_out.blif, xxx_yosys_out.blif, xxx.blif , xxx.net or fabric_netlist.v file?

@Baungarten-CINVESTAV Can you check if the post-synthesis netlists from Yosys is correct or not? This will help us to spot the bug.

Hello,

I have checked all the .blif files and their boolean equations are correct, to test the blif file, I developed a matlab script that takes the blif file and gets the SOP boolean equation for each output, then I compared the result of the boolean equation with a golden variable that stores a 128 bit sum. I did the same with the 3 blif files and everything works fine.

I also developed a testbench of the adder_128_with_vector_output_verilog.v (The verilog file made by yosys based on the .blif file) and the result was the same the module develops well the sum.

What do you think is the problem?

This issues was solve in #880, Summary, icarous verilog has some flaws.