netlistsvg

netlistsvg copied to clipboard

netlistsvg copied to clipboard

draws an SVG schematic from a JSON netlist

Exported svg is using "physical wiring connections" instead of "signal name association" (netlists)

I sucessfully converted my verilog `.v` electronics design to `.json` and then in a `.svg` file but I see that all the connections are drawn using the _"physicall wiring connections"_...

Is there a way to create a padding at the edges.... Sometimes my signal names get cut off it happens with signals `pcb_oscilator`, `pcb_spi_sck`, `pcb_spi_csn` and `pcb_spi_si` on the left:...

# Hierarchical netlists This adds support for hierarchical netlists (#64). It is now possible to show the inner schematic of the submodules. The settings for the hierarchy are controlled by...

In the following netlist, `A` and `B0` both should be connected to the output: ```json {"modules":{"module":{"ports":{"A":{"direction":"input","bits":[0]},"B":{"direction":"input","bits":[0,1]},"Y":{"direction":"output","bits":[0]}},"cells":{}}}} ``` but they are not! Instead, `B` is floating:  A more correct rendering...

**Input json file:** `{"creator":"Yosys 0.5+220 (git sha1 94fbaff, emcc -Os)","modules":{"gates":{"cells":{"and_2_1_1590516389917":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[3],"B":[1],"Y":[4]}},"and_2_2_1590516404134":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[5],"B":[3],"Y":[6]}},"and_2_3_1590516426292":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[7],"B":[6],"Y":[8]}},"and_2_4_1590516432644":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[9],"B":[5],"Y":[10]}},"PORT9":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"Y":"output"},"connections":{"Y":[9]}},"and_2_5_1590516445731":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[11],"B":[7],"Y":[12]}},"PORT11":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"Y":"output"},"connections":{"Y":[11]}},"and_2_6_1590516453833":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[13],"B":[10],"Y":[14]}},"and_2_7_1590516461836":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[15],"B":[8],"Y":[16]}},"PORT15":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"Y":"output"},"connections":{"Y":[15]}},"PORT16":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"A":"input"},"connections":{"A":[16]}},"and_2_8_1590516473667":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[17],"B":[13],"Y":[18]}},"PORT17":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"Y":"output"},"connections":{"Y":[17]}},"PORT18":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"A":"input"},"connections":{"A":[18]}},"and_2_9_1590516482679":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[19],"B":[4],"Y":[20]}},"PORT20":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"A":"input"},"connections":{"A":[20]}},"and_2_10_1590516492145":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[21],"B":[19],"Y":[22]}},"PORT21":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"Y":"output"},"connections":{"Y":[21]}},"PORT22":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"A":"input"},"connections":{"A":[22]}},"and_2_11_1590516499508":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[23],"B":[14],"Y":[24]}},"PORT23":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"Y":"output"},"connections":{"Y":[23]}},"PORT24":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"A":"input"},"connections":{"A":[24]}},"and_2_12_1590516507992":{"type":"$and","hide_name":0,"port_directions":{"A":"input","B":"input","Y":"output"},"connections":{"A":[25],"B":[12],"Y":[26]}},"PORT25":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"Y":"output"},"connections":{"Y":[25]}},"PORT26":{"hide_name":0,"type":"$rec","parameters":{"WIDTH":1},"port_directions":{"A":"input"},"connections":{"A":[26]}}}}}}` **skin file** - /lib/default.svg **some debug info:** 1. The issue is caused by net_13, below is the svg snippet...

I wanted to draw a page of a bigger schematic that would focus only on the SD card interface. Something like this:  Usually you have...

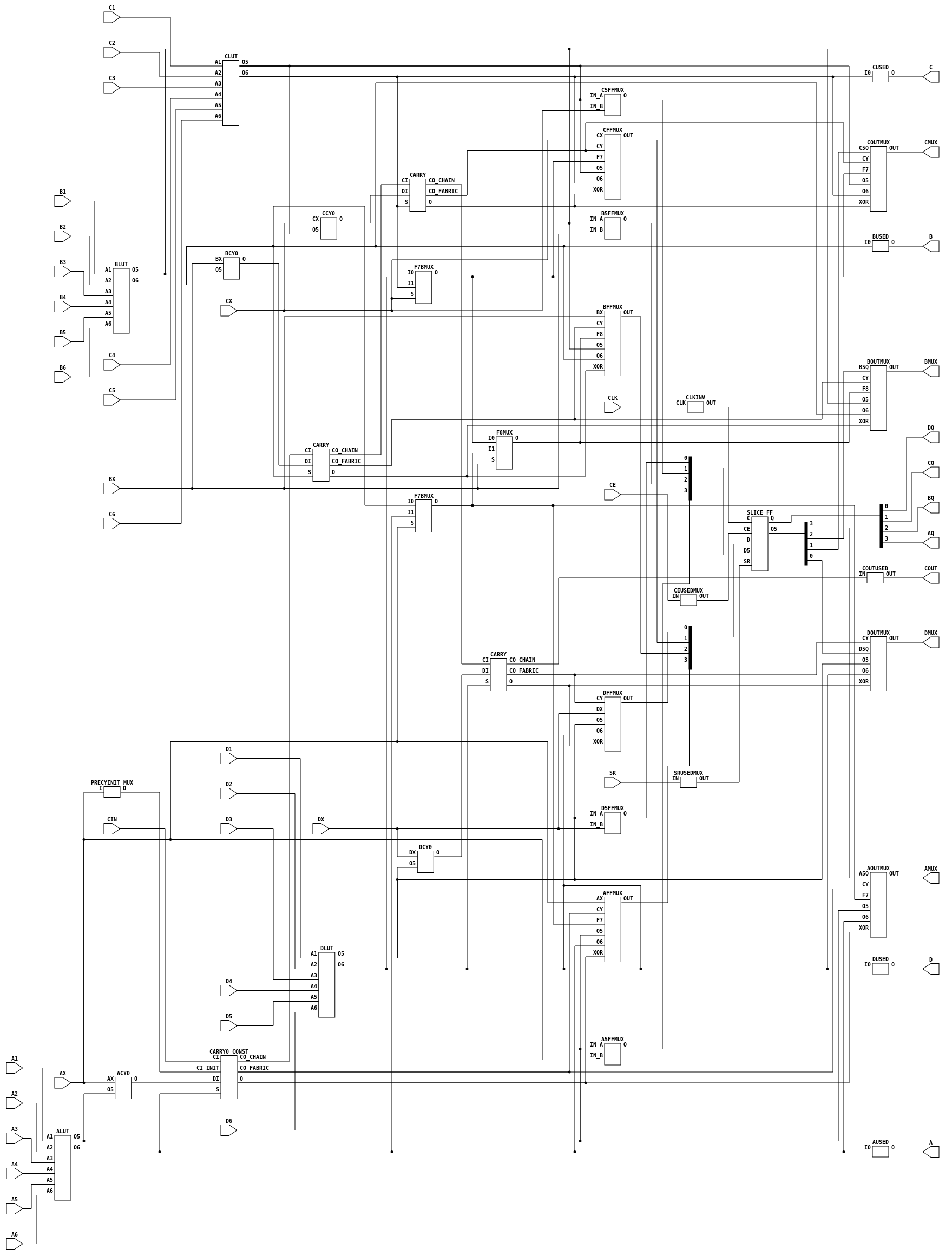

The json at https://gist.github.com/mithro/97fed031fe3fbbf5e2bf687bebf4e275 produces the following diagram;  I'm trying to figure out why it decided to place the `DLUT` at the bottom of the image near the `CARRY0_CONST`...

I really want to label my chips beyond the reference designator. Note (which should prevent merging this as is perhaps): If the value is empty now, you'll get this blank...

allowing multiple aliases for the same symbol allows us to not duplicate the same symbols for every name that yosys might give it. Having different cell types with different port...

Looking at the [ELK page they have this diagram](https://www.eclipse.org/elk/);  Looking at the channel 1 and channel 2 sections, this diagram shows support for "diagram inside a diagram" type thing....