Xiaohui Duan

Xiaohui Duan

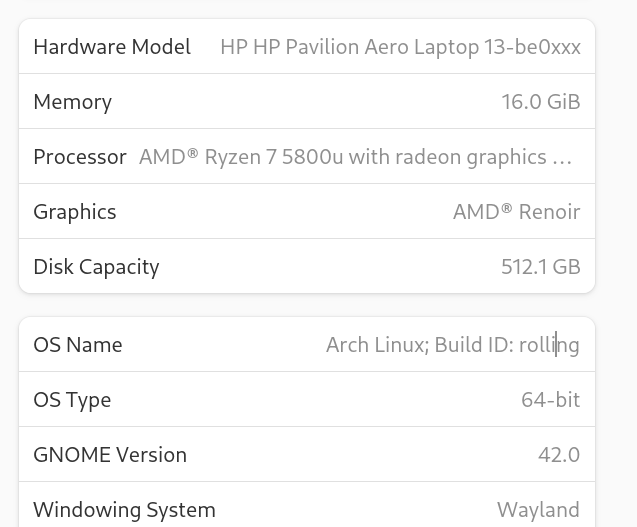

> * Does this problem occur by any chance on a high-resolution (4K) screen? Screen: 4K, 32 inch (should not configure scale at that PPI) > * Do you have...

And I also reproduced the problem on another screen, which is faked to be at 96 PPI.   xrandr output: ``` Screen 0: minimum 16 x 16, current 2560...

> @dxhisboy Could you tell me where to put the code you showed to fix the problem. I am using Ubuntu 20.04.4 LTS. > > Thanks I almost forget it,...

检查一下你的粘贴板是不是没有bmp格式? 用`xclip -o -t TARGETS -selection clipboard`检查一下。 比较小众的DE和原生GNOME会有这个问题。 一个办法使用gpaste的daemon,GNOME直接打开,其他DE的话可以单独运行daemon。 如果主要是为了粘贴截图的话我实现过基于GTK创建bmp粘贴daemon的方法,参考gitee.com/swmore/gimcopy

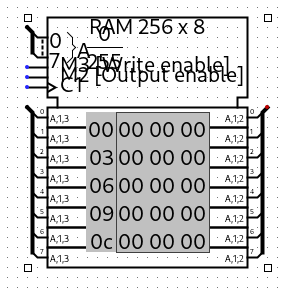

Also, a minor problem is: For a RAM with 256 entries, it generates: ``` TYPE byteArray IS ARRAY ( 256 DOWNTO 0 ) OF std_logic_vector( 7 DOWNTO 0); ``` But...

> @dxhisboy : Concerning your first remark: This is wanted behavior, as the RAM components normally should be operated with a clock component, and not, as you do, with an...

> The reasoning here is following: > > 1. in logisim a logisim clock cycle takes at least 4 real clock cycles. > > 2. FPGA's have only synchronous RAM...

Also, it seems asynchoronous RAM is not currently supported by logisim, in `RamHdlGeneratorFactory.java`: ``` @Override public boolean isHdlSupportedTarget(AttributeSet attrs) { if (attrs == null) return false; Object busVal = attrs.getValue(RamAttributes.ATTR_DBUS);...

I tested to move the dataOut path out of clock controlled region in RAM: ``` ARCHITECTURE platformIndependent OF RAMCONTENTS_RAM_1 IS -------------------------------------------------------------------------------- -- Here all private types are defined -- --------------------------------------------------------------------------------...

In my opinion, allowing the "gated clock" condition would allow FPGA experiments done in a step-by-step way (connecting the clock pin with a button), which is valuable for educational purposes....