blog

blog copied to clipboard

blog copied to clipboard

My blog

# 01_Makefile_makefile_summary A project has innumerable source files that are organized along various paths based on type, function, and module. The rules in the makefile state which files should be...

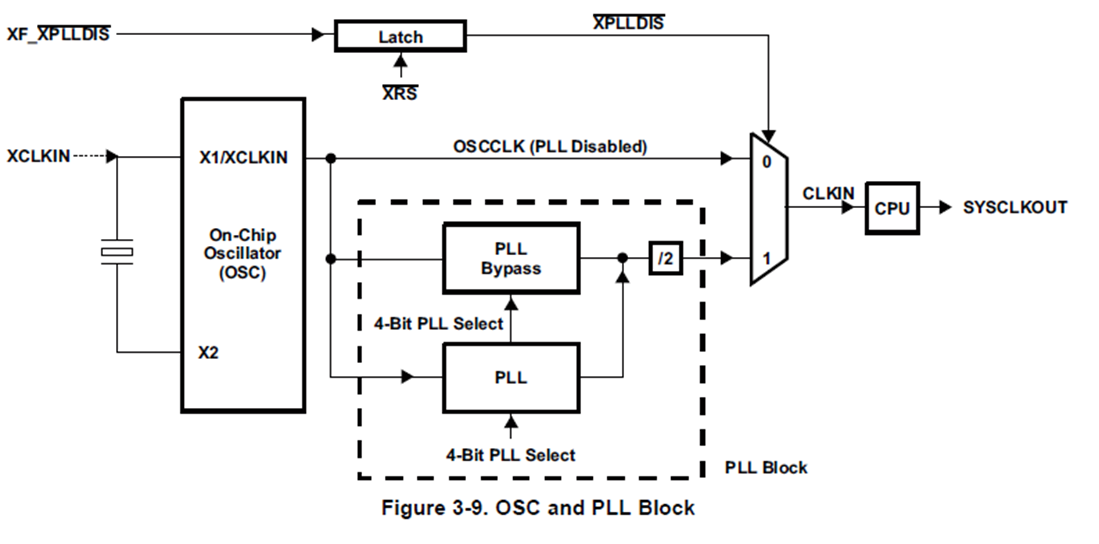

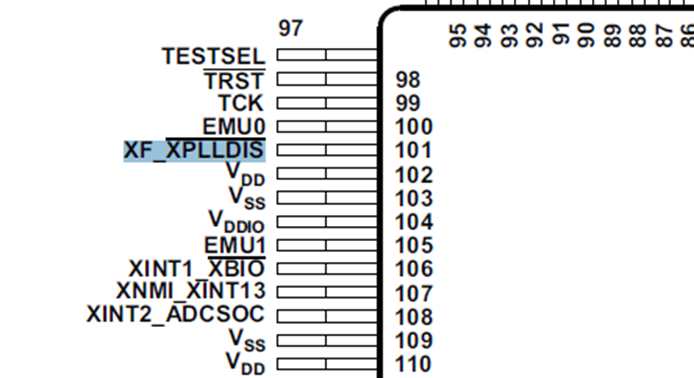

# DSP-F2812的时钟和系统控制 # 1振荡器OSC和锁相环PLL DSP里面肯定有时钟,没有时钟DSP怎么工作?这个我从时钟怎么产生的开始解释,咱们了解了解是有好处的。首先两个概念,振荡器和锁相环。(振荡器:(oscillator):是一种能量转换装置——将直流电能转换为具有一定频率的交流电能。其构成的电路叫振荡电路.晶振),(锁相环:(phase Locked Loop):是一种信号处理设备-------简单的说就是能将信号同步,相位统一达到同步的效果!) 其实,原理就是,由振荡器产生信号,但是产生的信号不同步,所以用了个锁相环把信号的相位弄一致,这样频率一样,幅度一样,相位也一样就形成了同步的时钟信号。 看一看F2812里面是怎么设计的呢?  左边是振荡器,邮编是PLL,两个联合成为时钟的生成装置。看一看,未处理的时钟信号从振荡器出来,分成三个路线,第一个路线直接出去,第二个是PLLBypass,PLL旁路,第三个叫PLL。然后我们来研究一下这几个有啥作用。最后的CLKIN和从振荡器出来的XCLKIN有啥关系呢。我们通过XF_PLLDIS(下图)  第101引脚,看到了吧。设置时钟的关系,XF_PLLDIS引脚。如果这个引脚禁止,就是使能PLL模块,直接用的就是振荡器出来的时钟信号,也就是XF_PLLDIS = 0;。如果XF_PLLDIS为高电平,PLL被使能,则表示振荡器产生的时钟要经过PLL模块。但是上图1-1明明PLL引出了两个引脚是不?那么到底选哪个?是PLL旁路还是直接PLL。当然啦,肯定有方法,PLL的控制不光是这个一个,这个仅仅是个使能位置,而已。我们需要进一步的设置一个寄存器,PLLCR,控制寄存器来有效的改变是选用哪个方式。(下面是原版英文) > The on-chip oscillator circuit enables a crystal to be attached to the F281x and...

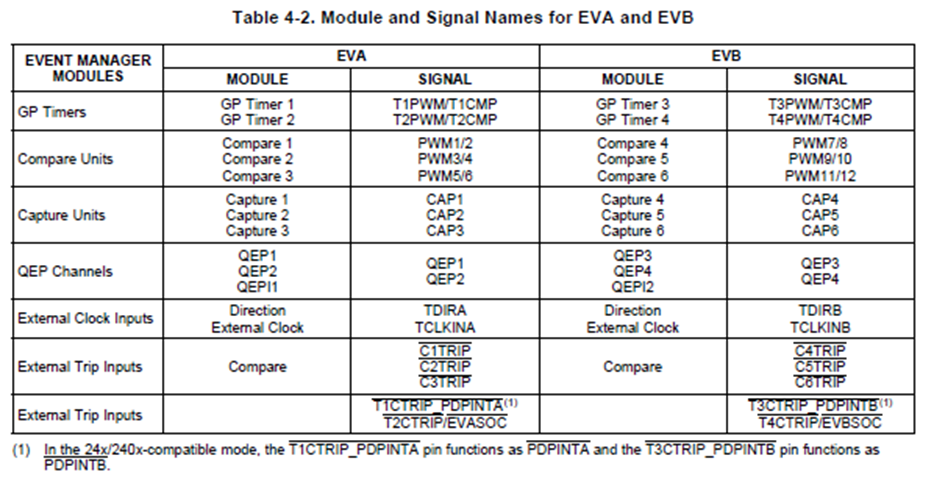

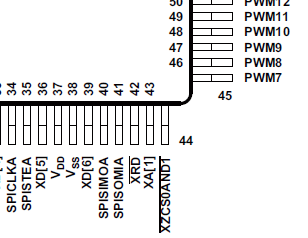

# DSP-F2812的事件管理器EV 2014年5月2日, 于沈阳化工大学 5号楼 明天就是五一了,本想在五一前夕把F2812有关的基础知识和原理总结完毕,没想到事儿太多,四月的最后一天还在整理事件管理器EV,进度差了,得抓紧时间了。时间管理器的页码很多,有关于它的资料也是很丰富的。第二次的学习,相信你与我一样,都有收获。 事件管理器,名字是事件管理,我们猜测就是跟发什么事儿有关,然后这个事儿有特定的管理机制进行管理。那些事儿是什么事儿呢?我们先放一放。首先呢,我先说个东西PWM波,这个东西就是个方波,但是高低电平的时间并不是一致的,是按照占空比来算的。这个东西有啥用呢?PWM波据我所知能进行的就是电机的控制,电力调速的,它的发现肯定节约能源。事件管理器的功能之一就是PWM波的产生,它可以有好几种方式产生PWM波呢。 我先说说EV要说些什么。首先本模块包括定时器(CPU也有,它也有),全比较/PWM单元,捕获单元,正交编码脉冲电路。共四大天王,组成EV家族。功能是相当强大。而最重要的EV的功能就是产生PWM波,四大天王各有各的功能,以自己的方式产生PWM波。 ## 1. 事件管理器的功能 DSP有两个EV,EVA,EVB,两个EV除了名字不同之外其他的功能是完全一样的。所以我们只说EVA,然后EVB我们就可以把EVA的原理对称过去。 EVA包含2个16位的通用定时器,3个比较单元,3个捕获单元,1个正交编码电路。我分别解释下四大天王: * 通用定时器:CPUTIMER0,1,2也同样是定时器,这个通用定时器和CPU定时器是两个东西,但是它俩的原理相似,区别在于CPU定时器为32位的,通用定时器是16位的,然后时钟不一样,工作方式也不一样,而且EV的通用定时器除了能计时之外,每一路还能产生单独的PWM波形。(高级了是吧!) * 比较单元:他就是上面说的【全比较/PWM单元】,名字中携带PWM单元,看来是产生PWM的主力,每个比较单元可以产生一对(两路)互补的PWM波形。3个比较单元就可以产生6路。正好可以驱动一个三项全桥电路。(一会儿讲解) * 捕获单元:功能就是捕获外部输入脉冲波形的的上升沿或者下降沿,可以统计脉冲的间隔,也可以统计脉冲的个数。通常用来对外部硬件信号的时间间隔进行测量,利用6个边沿检测单元测量外部的时间差,从而可以确定点击转子的转速。看来它的功能就是用来测量的。 * 正交编码电路:可以对输入的正交脉冲进行编码和计数,它与广电编码器项链可以获得旋转机械部位的位置,速率等信息,也用来电机控制。 看来四大天王各有千秋,通用定时器是用来计时而且产生PWM波也可以顶一顶。最多能产生4路。EVA两路,EVB两路。比较单元是PWM的主力,一个比较单元就能产生两路互补的波形,3个比较单元就是6路,再加上定时器的,一共可以产生16路。捕获单元捕获上升沿或者下降沿来捕获点点击的转速,是对PWM的测量。然而正交编码电路的也是测量功能,他的方式是对电机本身的,获取物理位置速率等信息。有可能是设置在反馈身上。 EV占用的管脚真的很多,四个通用定时器就能单独产生4路PWM波形,肯定就占用了4个引脚,比较单元更多了能产生12路呢,至少得有6个引脚啊。捕获单元同样6个,正交编码电路也得有6个。除此之外这只是功能引脚还得有其他的,包含一些,终止引脚。  ### 1) External Cmpare-output Trip Inputs...

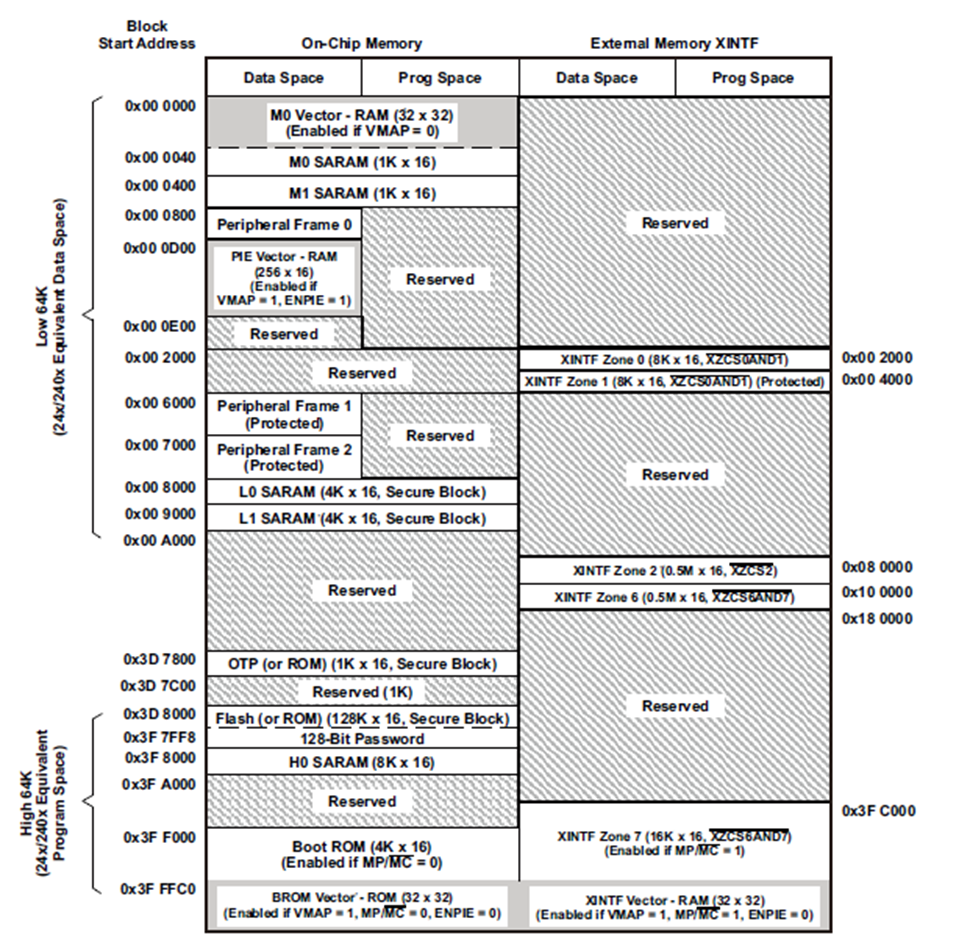

# DSP-F2812的CMD文件 我们编写F2812文件的时候必须要添加一个CMD文件嘛!那个CMD文件的作用就是把结构体编写的文件映射到DSP内部的内存中。之前我们通过结构体和共同体的方式定义了很多的寄存器,通过语言就能控制寄存器,然而定义那么多只不过是个规则而已,只是空洞的字母,CMD文件的作用就是把定义那些空洞的字母和内存里面的地址链接起来,这样我们通过控制那些字母就能控制寄存器了。 流程:硬件 --> CMD文件 --> C链接文件 --> 头文件 --> 程序代码 Memory Map:  上面是F2812的存储映像图,我们怎么来写CMD文件,首先,我们得弄清楚点儿东西 > 存储器的种类: > > 一、补充点儿知识:咱们按照这么分:RAM和ROM和FLASH > > RAM: > 1. SRAM:静态读写存储器,速度快,容量小,断电后数据丢失。可读可写。 > 2. DRAM:动态读写存储器,速度慢,容量大,断电后数据丢失。需要刷新电路。可读可写。...

# ELF文件---目标文件格式 ## 1. 概述 有几个涉及的专有名词概念 * 段(segment)/节(section)单位存储到elf文件中 * 代码段(code section): .code 或者 .text * 数据段(data section): .data 这里面有几个一般性的规则: * .bbs段是存储全局变量和局部静态变量未初始化的。 * .data段存储 已初始化全局变量和已初始化局部静态变量的位置。 * .指令、函数调用、局部变量都存储在.text段(局部变量吃栈空间) ```C int a =...

# DSP-F2812的串行通信接口SCI 今天是五一假期的最后一天,虽然是以清明节的名义放的假,但是觉得放假还不如不放假,放假了学校轻易的给停电,影响了进度。关于DSP我们还差两个外设模块没有整理,现在正在筹集DSP最小系统的各个部件,今天还算是有时间,把SCI模块总结下来! -----------2014.5.4,沈阳化工大学,5号楼 ## 1.SCI模块的概述 SCI(Serial Communication Interface)的简称,就是我们说的串口。但是串口有两种形式,一种是同步的形式,另一种是异步的形式。我们的SCI模块就是异步的形式,就是不需要同时发送或者同时接受。在任何时刻都能进行发送或者接收。在结构上SCI具备了两条线,一条是SCI的发送线,一条是SCI的接收线,可以理解为,SCI的上传和下载功都是分开的,互不干扰。X2812xSCI模块采用NRZ标准格式的异步外围设备,只要遵循这样标准的串口都能进行数据通信。当初我理解串口的时候有个误区,就是串口就是RS232的那种接口。其实不是的,串行数据可以设置成人和的接口,只要是有支持那样的芯片,我们可以用RS232,那么中间需要的芯片是Xlini公司的MAX3232芯片进行中转,我们同样也可以做成通用USB,只是中间的芯片需要更换一下。 X2812x同EV一样,都集成了两个分立而不分开的模块,SCIA,SCIB,还有SCI是需要存储的,即一定要有一个16级深度的FIFO队列。记得ADC中存在一个2级深度的FIFO堆栈。这个SCI拥有的是一个16级深度的FIFO堆栈,而且他们有自己的中断。SCI的工作方式,有三种模式,单工,半双工,全双工模式。 >4.6 Serial Communications Interface (SCI) Module The F281x and C281x devices include two serial communications interface (SCI) modules. The SCI...

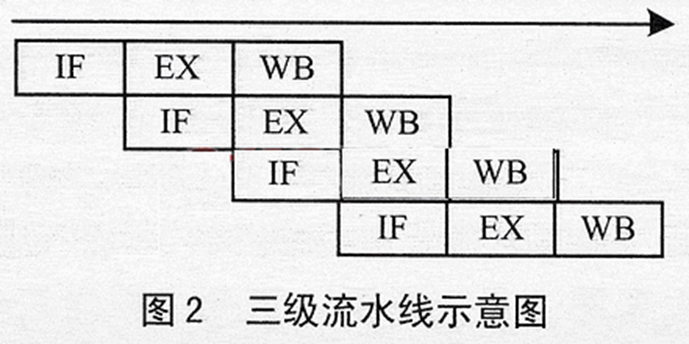

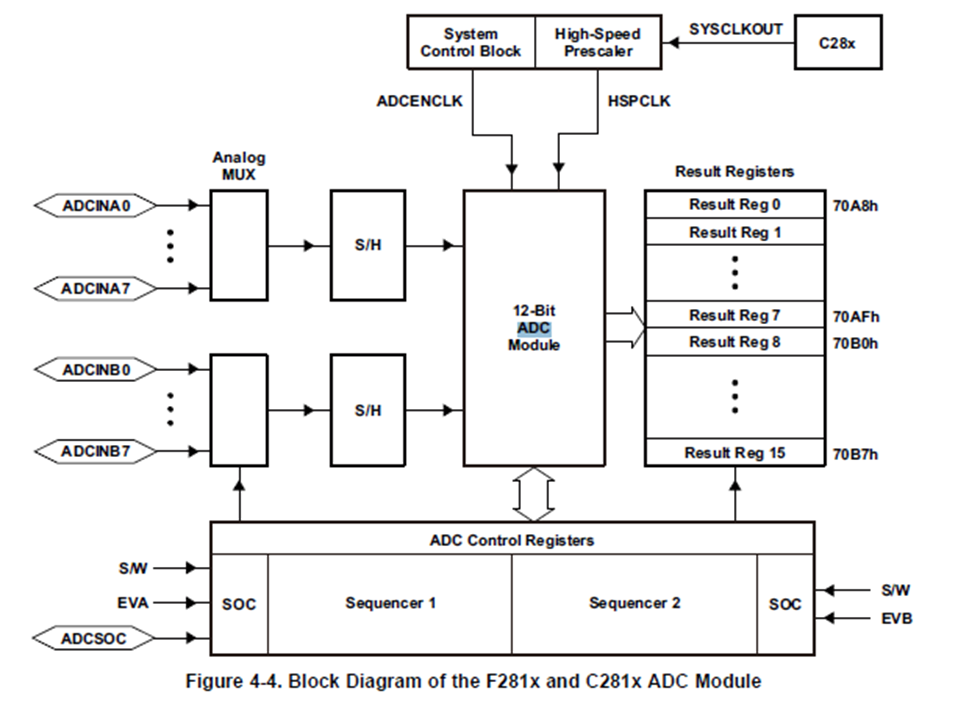

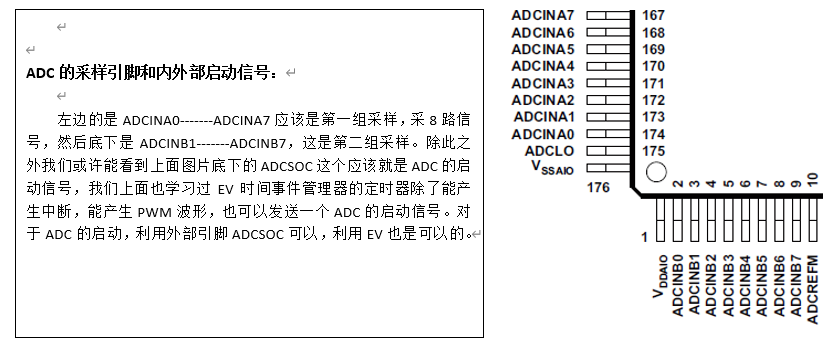

# DSP-F2812的模数转换器ADC 2014年5月3日,于沈阳化工大学,5号楼 ADC是很重要的外设,今天我们得重视,这个东西嘛。本身还是很好学的,只是我们要有耐心就好了。会了基础,剩下的就是做工程的时候灵活应用,基础是死的,可人的思维是活得。我们充分利用好每个功能哦。 工程,总得感受外界的东西。只有感受到外界的东西,我们才能进行处理,数字化是种进步,当我们发现了某种规律和数学有着各种各样的联系才能为我们造福。数字信号处理,数字电子技术中,都存在着一种模数转换,数模转换的概念。我们已经很清晰了,外界的信号是模拟量,也就是连续的信号,声音,温度等。在数学上这些模拟量如果转化到数字的世界,他们之间的间距是无穷小的,根本就无法运算。可是奈奎斯特发现了采样定理,使我们进入了一个数字化的世界。采样定理就是我们采样的频率不能少于二倍的信号本身的固有频率,这样我们可以轻易的从模拟转换成数字,又从数字还原到模拟。我们能做的,就是利用各种数学关系去计算中间的数字化的信号。这个过程就是数字信号处理。而现在,我们要通过DSP的ADC功能将外部的模拟信号采集进来,然后再利用我们的数学算法进行信号处理,然后再数模转换输出应用于世界的模拟信号,达到预期的效果。今天本节就是说一说模数转换器ADC。怎么外来世界采入信号到DSP呢?我们一步步的说。 ## 1. X2812x内部的ADC模块 X2812x内部的ADC模块是一个12位分辨率,具有流水线结构的模数转换器。(这里面有两个概念,第一个就是12位分辨率,和流水线结构)。 >有关于分辨率的参考文献: 举个例子,假设一个模拟模块的输入电压范围是0~10V,而该模块的分辨率为10位,2的10次方=1024,则该模块所能识别的最小电压等级为:10/1024=0.009765V,即电压每增加0.009765V,数字量增加1。所以位数越大精度越高,运算量就越大,运算时间越长,根据自己的需要选位数,不是位数越多越好。 > >模拟量输入模块有两个参数容易混淆: > 1.模拟量转换的分辨率 > 2.模拟量转换的精度(误差) > >分辨率是A/D模拟量转换芯片的转换精度,即用多少位的数值来表示模拟量。S7-200模拟量模块的转换分辨率是12位,能够反映模拟量变化的最小单位是满量程的1/4096。模拟量转换的精度除了取决于A/D转换的分辨率,还受到转换芯片的外围电路的影响。在实际应用中,输入的模拟量信号会有波动、噪声和干扰内部模拟电路也会产生噪声、漂移,这些都会对转换的最后精度造成影响。这些因素造成的误差要大于A/D芯片的转换误差。(百度空间) > 流水线结构: > 系统在处理数据的时候,一个指令周期含有4~6个时钟脉冲,每个脉冲周期由不同的部件完成不同的操作。非流水线结构是指一个指令周期完成以后再接受下一条处理数据的指令;而流水线结构,每个时钟脉冲都接受下一条处理数据的指令,只是不同的部件做不同的事情,就象生产线流水操作一样,并不是等一个或一批产品做完,再接受下一批生产命令,而是每个工序完成以后,立即接受下一批生产任务。这样提高了系统处理数据的速度 > >  明白了分辨率和流水线结构。我们就来说说这个ADC模块。  最左侧的是ADCINA0…ADCINA7,和ADCINB0…ADCINB7,共16路采样,看来这个就是个引脚了,也就是要采什么,就把什么东西放在这个引脚上。我们看看在DSP上这几个引脚都在哪里! ...

# DSP-F2812的中断系统 2014年5月1日,于沈阳化工大学,5号楼 第一次接触中断概念还是在C51单片机中,那时候讲的中断就是很简单的一个功能,LED的点亮,后来在图书馆借书发现真的好多程序在中断中可以执行的。那时候发现啊中断真是个重要的概念。后来我C51就放弃了,很久一段时间我开始接触2812这个概念又一次的出现,或者吧,中断是在MCU中的一个重要的思想。X2812的中断系统,我们再一次的学习,现在我就要进行一个整理,算是我对X2812的一个理解。 ## 1. 什么是中断 中断是个通用的概念,任何MCU中都会有中断系统。给举个生活中的简单的例子,我正在打字,然后电话突然响了,然后我停下手中的工作去接电话,然后处理一些事情,电话结束,然后我继续打字。我在举一个软件中断的例子,我写了一段C语言的代码,里面当然有必要的main函数,还有我定义的add()函数,我开始在main函数中赋值,然后就执行了add()函数,以下例子: ```C #include int add(int,int); void main(void){ int a,b,c; a = 1; b = 2; c = add(a,b); a = 2; b =...

# DSP-F2812的CPU定时器 2014年4月25日,于 沈阳化工大学,5号楼 我一开始的时候把定时器和时钟弄混了,以为是一个东西,这个问题多么的幼稚啊。其实是自己学的太着急了,很多东西都一起看,结果,结果就学的洗了糊涂。学习本来就是一个熟悉的过程,需要时间来将它理解。太急了肯定不行,所以要放慢脚步,仔细读你当前的东西。也许就会发现,我学到的,是这么的多。 ## 1. CPU定时器工作原理 > CPU-Timers 0, 1, and 2 are identical 32-bit timers with presettable periods and with 16-bit clock prescaling. The timers have a...

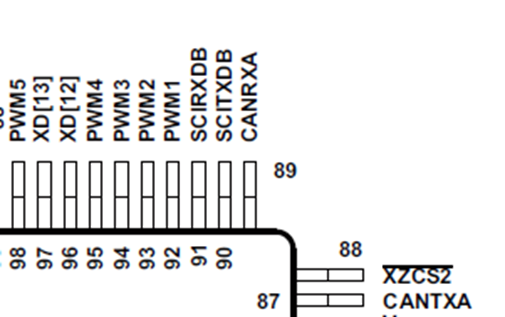

# DSP-F2812的通用输入/输出多路复用器GPIO 2014年4月24日,沈阳,5号楼 ## 1. GPIO多路复用器 多路复用的意思很明白吧,就是一个引脚有好几个功能。我又一次惊叹了,本来DSP引脚就跟蜈蚣似的,再复用,那岂不是更多功能了。说也是,但是人家TI就是这么设计的,我们必须要遵从这个规则,而且,还要明白,这个是怎么用的。废话不多说了,进入正题。 GPIO是多路复用的意思,也可以做功能引脚,也可以做I/O口,I/O口的意思就是输入输出口,那就说明DSP可以输入可以输出,可以吞吐。那么功能引脚是什么呢?功能引脚很简单了,就是有一定功能的引脚呗。比如说,咱们的EV,SCI,SPI,ECAN,这些丰富的外设,我们想要用这些这些功能的时候,相应地通过外部的一定控制来进行使能,所以就是功能引脚。比如举个简单的栗子,SCI,异步通信接口,这个很通用是吧,这个引脚的名字是:右图所示,一个SCI发送使能引脚,一个SCI接收使能引脚。我们用它来实现SCI的发送和接收的功能。同样滴,这两个引脚可以做通用的I/O口。是不是很神奇。背后的操纵一会儿再说,我们知道了,这个引脚是有两个用法的,一个是功能引脚,一个是通用I/O口。 一下图片是从DSP上面截下来的,是为了让我们更清晰的看见什么是GPIO。这里有一些是GPIO,    有以下不是GPIO,但多数都是,PWM肯定是啦,CAP那个也是,SPI也是。 ## 2. GPIO的寄存器 GPIO就是I/O引脚的管理机构,它能够管理I/O引脚,召唤出I/O的功能。它的管理机制和理念就是,将56个引脚分成6组进行管理,分为GPIOA,GPIOB,GPIOC,GPIOD,GPIOE,GPIOF。也就是将这56个属于这个I/O的引脚分为了6组,而且这个6组的I/O引脚不是平均分配的,不一定是谁多谁少。他们分别是,16,16,4,3,15,2个引脚。 咱们首先想想,就跟设置东西似的,GPIO能设置什么东西,首先第一步,肯定设置什么引脚吧,那我的选择就是功能引脚或者I/O口呗。那么设置为功能引脚就没什么说的了,功能就固定呗,你是SCI就是SCI,你是EV就是EV。但是如果我选择I/O引脚,又出现两个分路口了吧,是输入?还是输出?对吧,要不然你怎么指定啥是啥功能呢?你说对吧。现在设置什么搞明白了,就开始怎么设置了。DSP的设置通常都是对寄存器进行设置,那么很简单了,我需要了解几个寄存器我就能对GPIO进行相应的设置了。 GPIO的寄存器分为了两种:第一种就是控制类的,包括功能选择寄存器,GPxMUX,方向控制寄存器GPxDIR,输入限定控制寄存器GPxQUAL。第二种就是数据寄存器,主要是数据寄存器GPxDAT,置位寄存器GPxSET,清除寄存器GPxCLEAR和取反寄存器GPxTOGGLE组成。 我先说说怎么记忆,然后再说说都是干啥的。 功能选择,顾名思义就是个选择功能呗,很简单,GPxMUX进行的设置就是这个引脚是IO口,还是功能引脚,举个例子,CANRXA引脚。是CAN总线的接收使能引脚,我查询一下CNRXA是那个GPIO组管辖之内的,现在去找那个表…..原来是GPIOF管辖的脚,现在知道它在GPIOF省了,那么它在哪个市是不是还要知道。哦,原来它在第7市,好了,我需要的信息就是这些了。然后我怎么设置呢?如下: ```c EALLOW; GpioMuxRegs.GPFMUX.bit.CANRXA_GPIOF7 = 1; // 0为I/O口,1为CAN总线的功能引脚 EDIS; ```...