riscv-isa-sim

riscv-isa-sim copied to clipboard

riscv-isa-sim copied to clipboard

[Bug Report] Wrong exception priority during access memory

Let's take the load instruction as an example:

https://github.com/riscv-software-src/riscv-isa-sim/blob/0f15aa09005a12521c27005515e088cbd1b81629/riscv/mmu.h#L99-L125

At line 101, load will first check if it is aligned, then at line 122 it will try to access the address in the load_slow_path function.

https://github.com/riscv-software-src/riscv-isa-sim/blob/0f15aa09005a12521c27005515e088cbd1b81629/riscv/mmu.cc#L142-L162

In load_slow_path, it will first check if it is legal address at line 153, and the watch point will be checked at the end of the function.

Briefly, the order of priority is as follows: trap_load_address_misaligned > trap_load_access_fault > trap_breakpoint

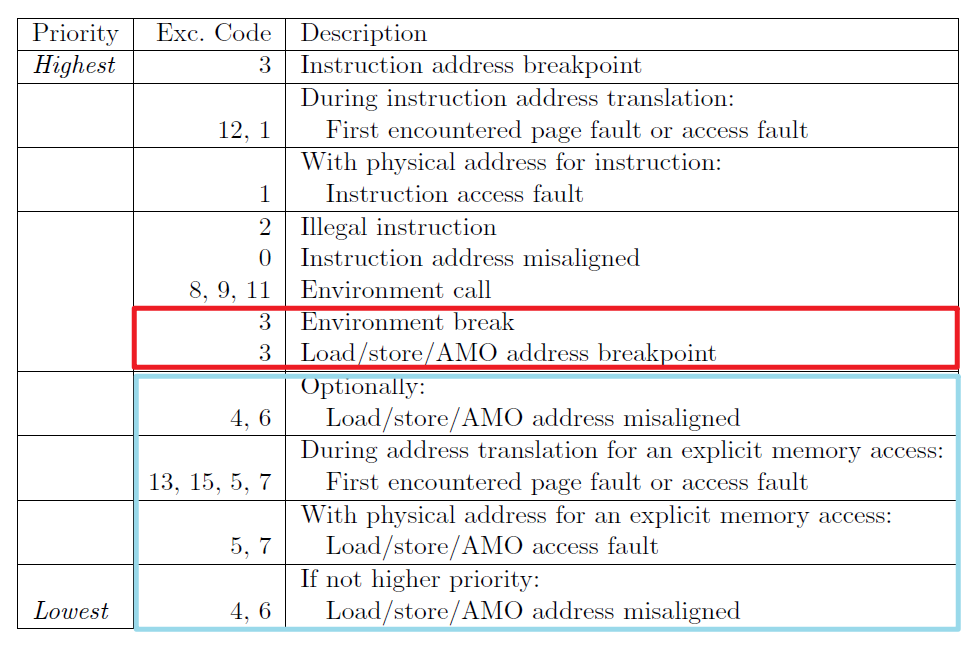

However, in the specification, trap_breakpoint has a higher priority than the others:

We also co-simulate with rocket to check this point, rocket threw a breakpoint exception, while spike threw an error misaligned exception. The test point is at 0x800001c0 where loading a misaligned illegal address 0x100004001:

3 0x00800001bc (0x7a261073)

core 0: 0x00000000800001bc (0x7a261073) csrw tdata2, a2

3 0x0080000004 (0x34302f73) x30 0x0000000100004001

core 0: 0x00000000800001c0 (0x00062603) lw a2, 0(a2)

core 0: exception trap_load_address_misaligned, epc 0x00000000800001c0

core 0: tval 0x0000000100004001

core 0: 0x0000000080000004 (0x34302f73) csrr t5, mtval

3 0x0080000008 (0x34202f73) x30 0x0000000000000003

core 0: 0x0000000080000008 (0x34202f73) csrr t5, mcause

[error] WDATA SIM 0000000000000004, DUT 0000000000000003

[error] check board clear 30 error

[CJ] integer register Judge Failed

I believe this is a duplicate of #538

Yes, but the priority of the misaligned exception is also wrong, which is outside of the load_slow_path function.

@timsifive perhaps this is of interest to you, since you're doing some trigger work now.

I agree that this is wrong, and a (exceptionally clearly described) problem. It's been a long time since I added that trigger code. I'm not sure how to raise the trigger priority while minimizing the performance impact.

I might have time to look at this in a few weeks, when I'm back from vacation.

@Phantom1003 can you confirm if #1105 fixed this for you?

Yes, the breakpoint can now be triggered successfully.