crbus_scripts

crbus_scripts copied to clipboard

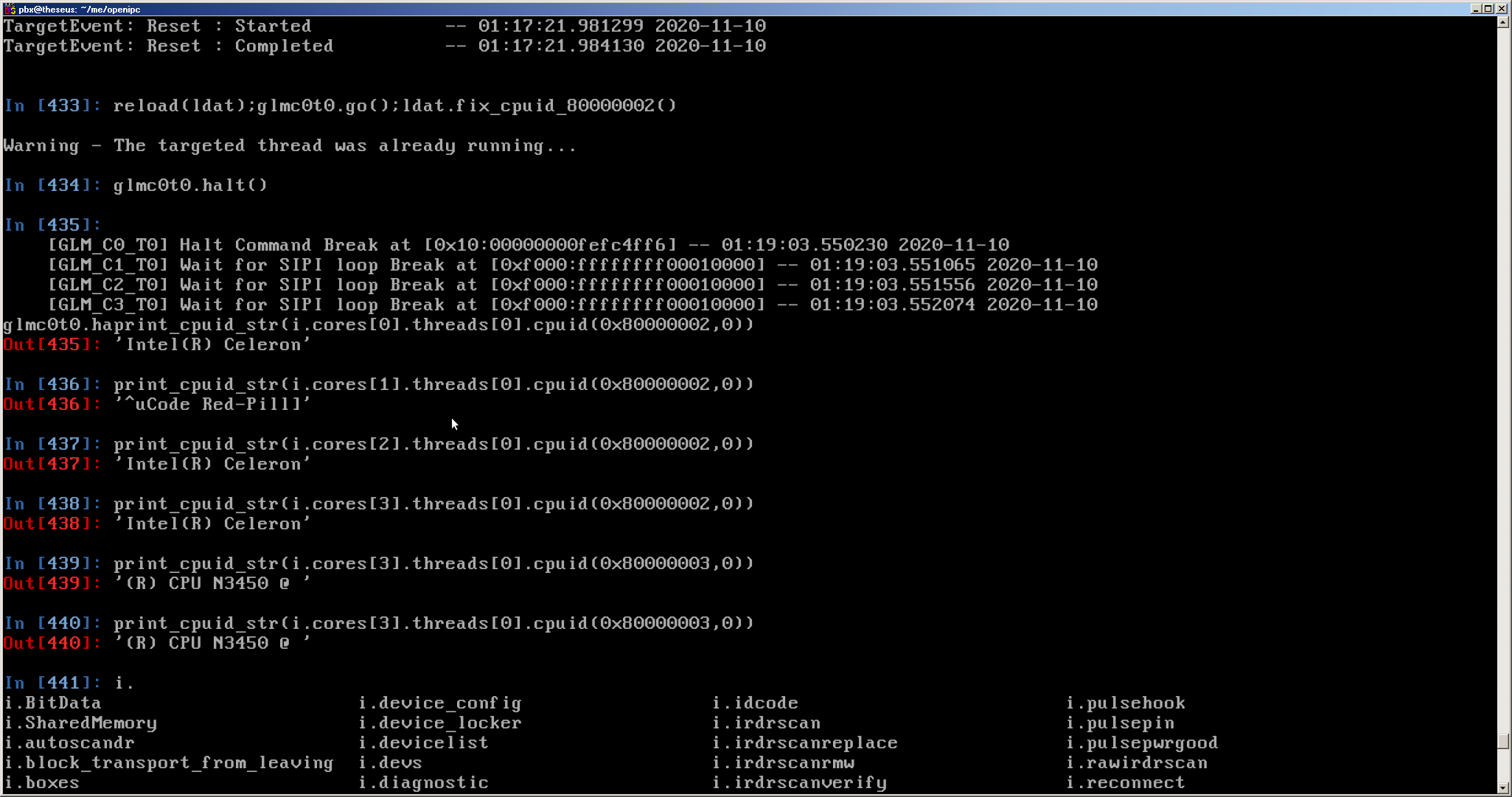

Only 1 of 2 cores in module affected in Celeron N3450, but demo works.

To anyone trying to replicate:

When trying the CPUID proof of concept on the Celeron N3450, only the second core is affected.

CPUID is Fam:6 Model:5C Step:9, uCode revision is 0x40 and ROM is byte for byte identical to the glm-ucode repo.

This SoC has 4 cores distributed as 2 cores per module. Any mistake during loading kills both C0 and C1 at the same time so they are linked, but changing the uCode of module 0 only affects C1, leading me to think nothing was happening for a long time before discovering my mistake.

Demo of it working, but only half:

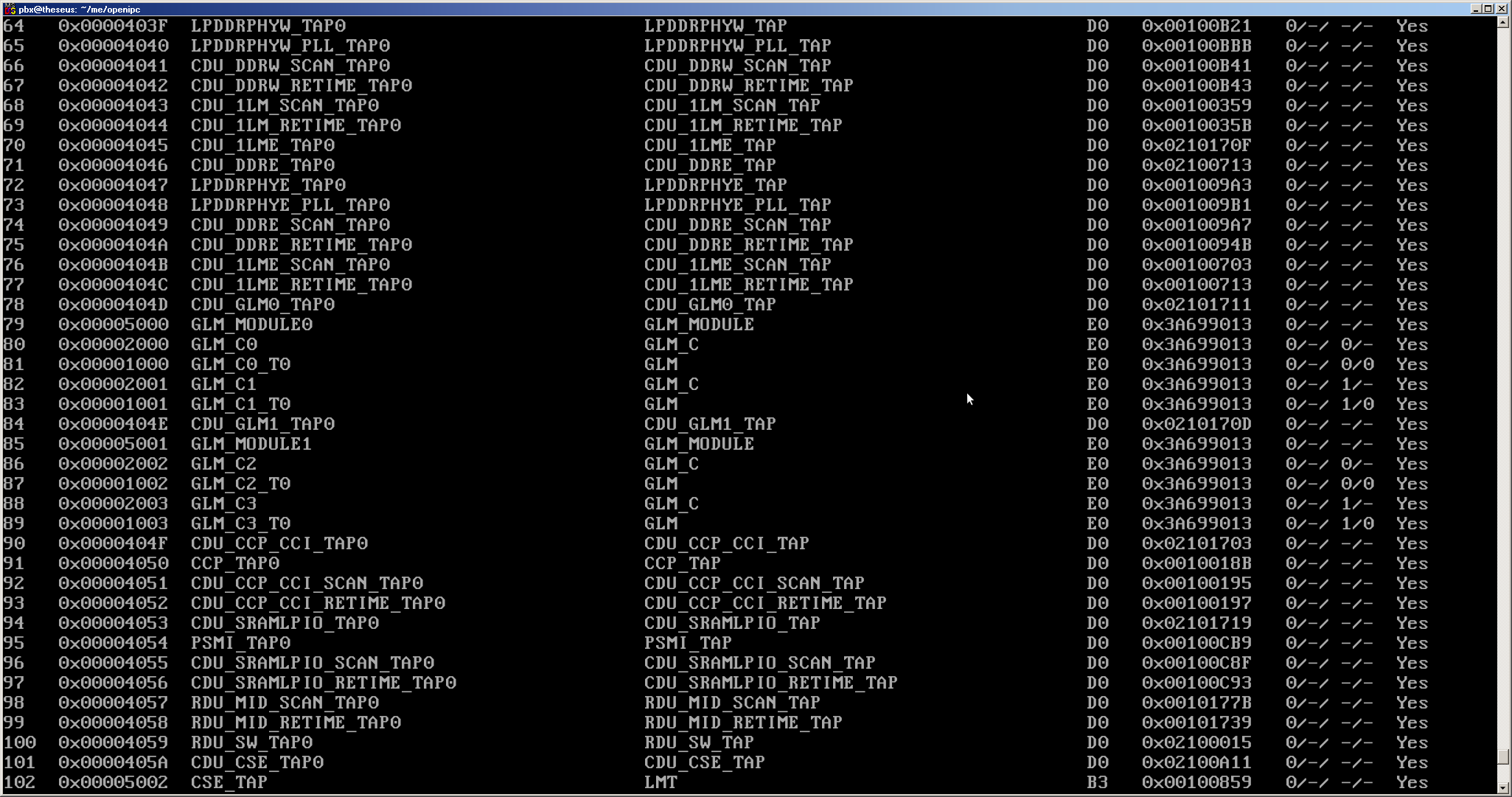

Partial device list showing core topology: