Phung Cheng Fei

Phung Cheng Fei

[axi_ram module](https://gist.github.com/promach/cdc4a26aa7dc03538918bbd85344cfb5#file-axi_slave_ram-v-L250) triggers a AXI protocol [violation bit 32 in Xilinx AXI Protocol Checker](https://www.xilinx.com/support/documentation/ip_documentation/axi_protocol_checker/v2_0/pg101-axi-protocol-checker.pdf#page=17) To be more exact, it is related to the `BVALID` logic implementation in the AXI slave....

Hi, I came across your winograd convolution article at https://antkillerfarm.github.io/dl%20acceleration/2019/07/19/DL_acceleration.html May I know what are ß0, ß1 and ß2 ?

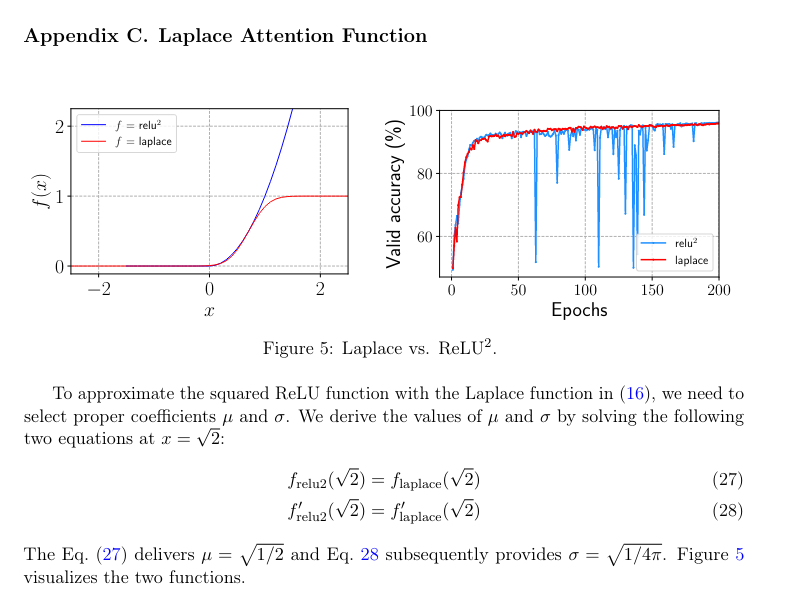

1. For https://arxiv.org/pdf/2209.10655.pdf#page=21 , why use `x = sqrt(2)` specifically ? why is it not easier to just use `x = 1` ?  2. In https://arxiv.org/pdf/2109.08668.pdf#page=5 , I do...