Virtual bus parsing bug for verilog

Hi,

I've just discovered your tool, and it looks very good ! I have some troubles getting the virtualbus feature to work though. It feel like the parser is not working as intended for Verilog :

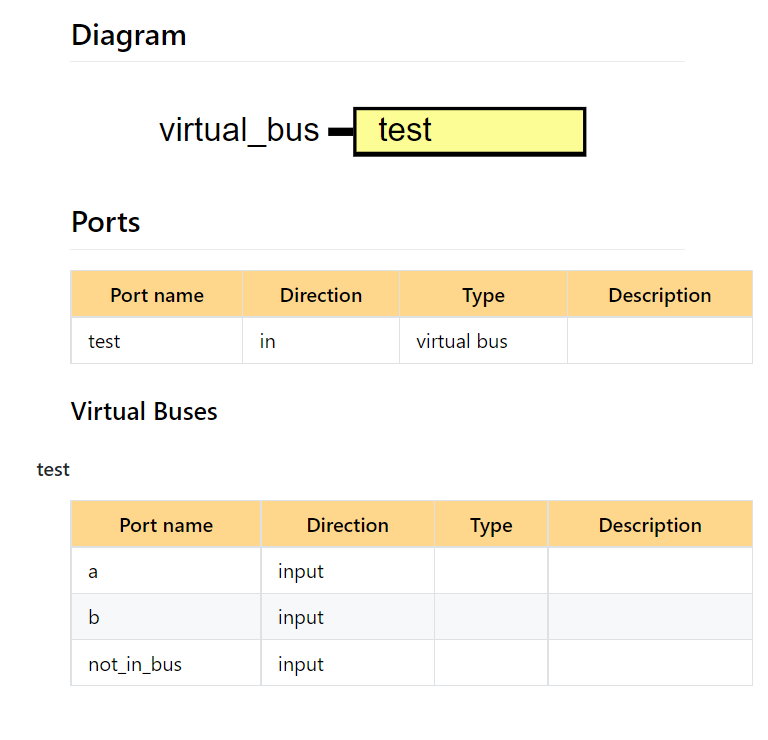

Case 1 : Just not working

module test(

//! @virtualbus test

input a,

input b

//! @end

);

endmodule

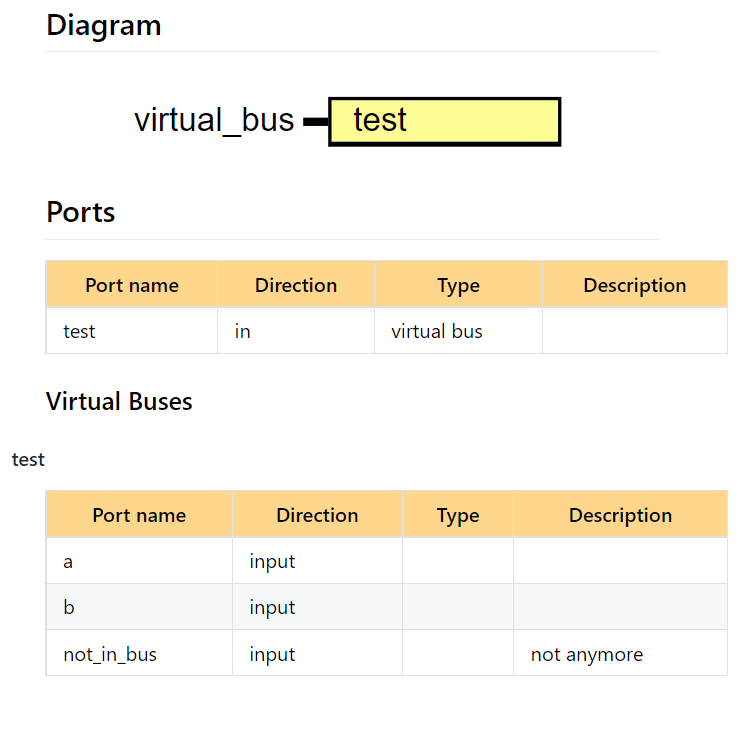

Case 2 : including a port which shouldn't be in the virtual bus

module test(

//! @virtualbus test

input a,

input b,

//! @end

input not_in_bus

);

endmodule

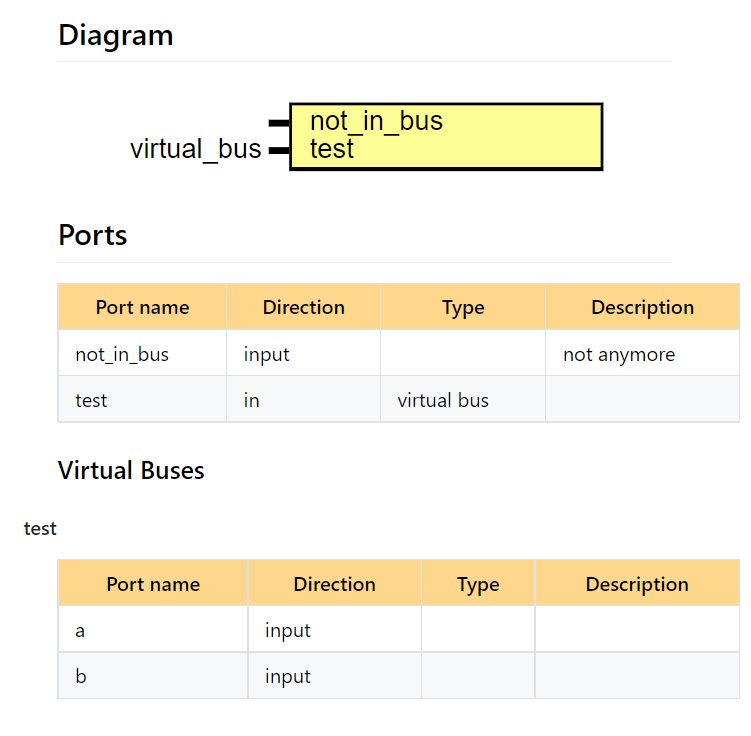

Case 3 : adding inline comment, now the virtual bus is missing again

module test(

//! @virtualbus test

input a,

input b,

//! @end

input not_in_bus //! not anymore

);

endmodule

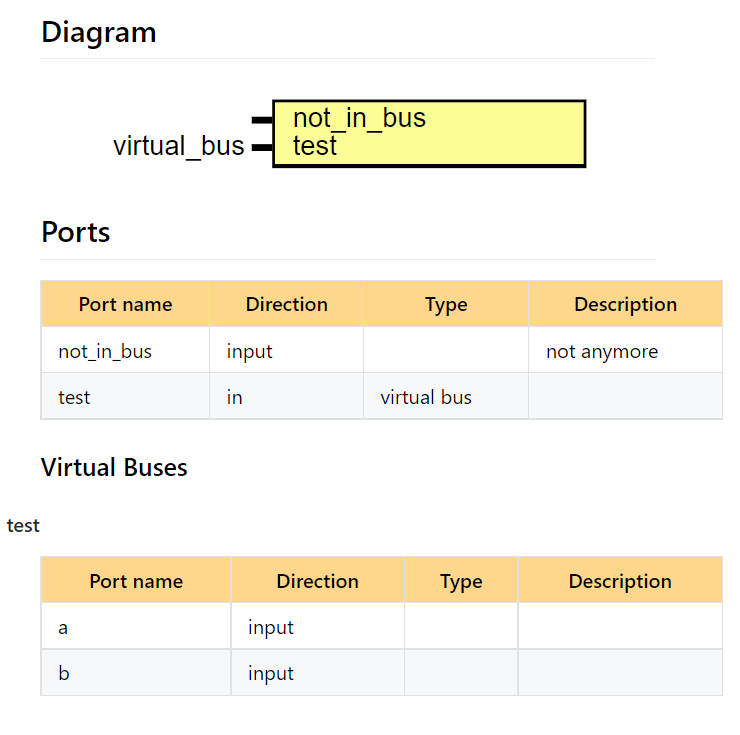

Case 4: but with multiline comments it goes back to case 2

module test(

//! @virtualbus test

input a,

input b,

//! @end

//! not anymore

input not_in_bus

);

endmodule

Case 5: working

module test(

//! @virtualbus test

input a,

input b, //! @end

//! not anymore

input not_in_bus

);

endmodule

Case 6: end above the last port of the virtual bus works correctly

module test(

//! @virtualbus test

input a,

//! @end

input b,

input not_in_bus //! not anymore

);

endmodule

TL;DR : the "end" tag seems to be grouped with the next following port, instead of the port right above it. This leads to problems if it's at the end (no port following it, so it gets dropped), or it can have wanky interactions with the next port (including an additional port into the virtualbus, not working at all, etc...). A solution is to 'force' the tag to be grouped with the last port of the virtualbus, either by putting it as inline comment (so to the right) or as multiline comment (so just above). This last solution is not nice visually, and don't follow the documentation : "All the ports between the lines: --! @virtualbus and --! @end will be grouped in the diagram and the ports table"

- OS: Windows 11

- VSCode version 1.66.2

- TerosHDL version : v2.0.6 (freshly installed from VSCode extension)

Thanks for the long explanation!!

Really this not a bug. A comment if associated to a port if it's inline or above the declaration. Here:

module test(

//! @virtualbus test

input a,

input b

//! @end

);

endmodule

"@end" isn't associated to any port. So you need to associate it to input b

module test(

//! @virtualbus test

input a,

input b //! @end

);

endmodule

or

module test(

//! @virtualbus test

input a,

//! @end

input b

);

endmodule

But your are right, it's a little confused. So I will change the label from bug to enhancement .

In that case, could you maybe also check if the same applies to VHDL ? Because the example code given in the documentation (https://terostechnology.github.io/terosHDLdoc/documenter/start.html) imply you can write the --! @end tag below the last port of the virtual bus. If it's a Verilog vs VHDL parsing difference, it would be very cool to have a page with all these subtilities :)

Also, the sample code is not producing the documentation as expected : there are 3 @virtualbus but only 2 @end (I guess there is one missing line 65), mem_dout is not drawn on the diagram and only 2 virtual busses are created in the documentation (even after adding the missing @end).

That being said, thanks a lot for this awesome tool ! :D

You are right. Quite a while ago I made some changes, but honestly I don't remember them... I will check it and I will improve the documentation. It will take a time, because I'm working in other stuffs, but I will do it.

Between "@virtualbus" you don't need to declare the "@end". E.g:

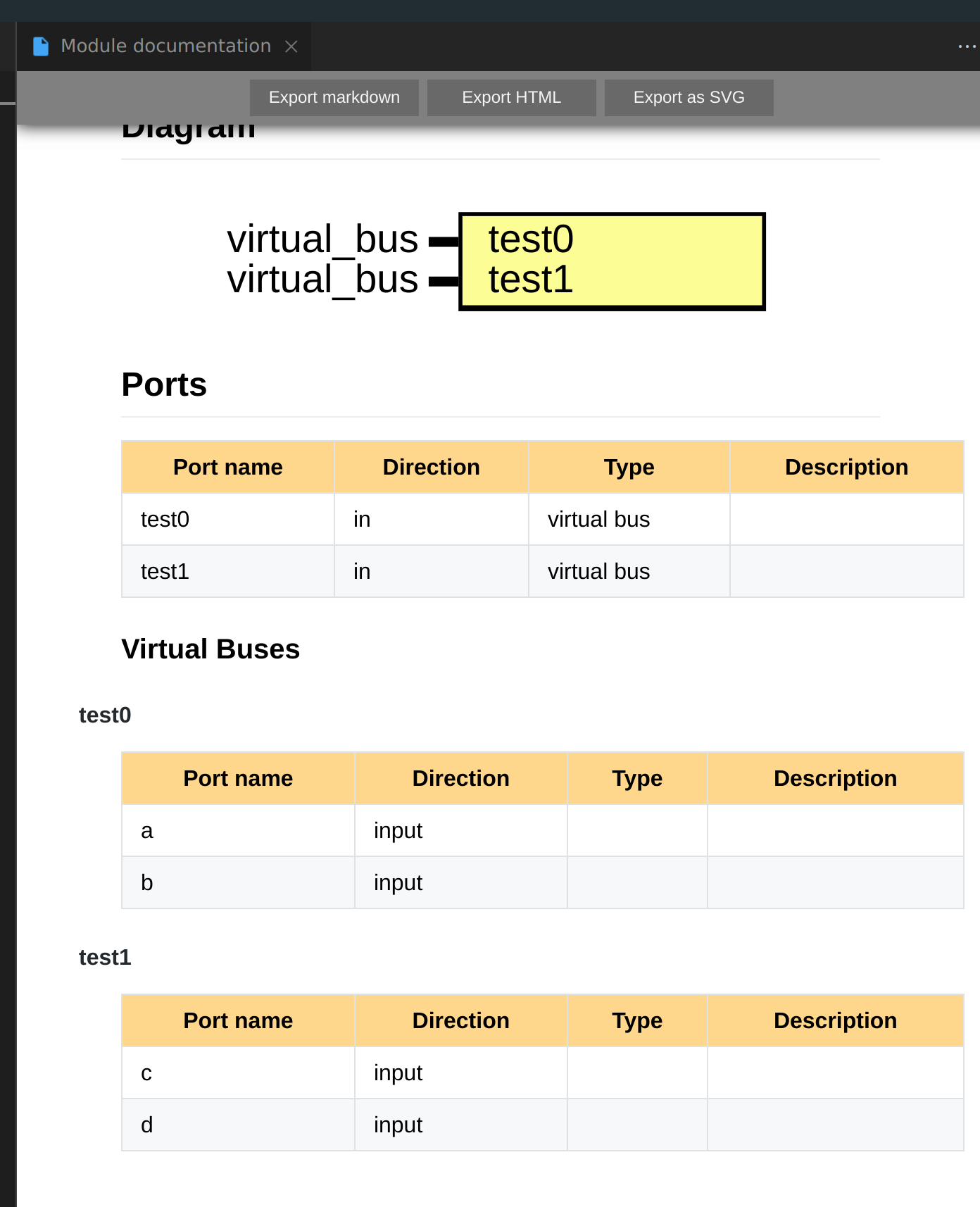

module test(

//! @virtualbus test0

input a,

input b,

//! @virtualbus test1

input c,

input d //! @end

);

endmodule

Hello! First of all ty for all the hard work done with this VS plugin.

Nevertheless though, I'd like to reopen the discussion on this "feature".

Suppose I want to add @virtualbus information to an entity/module with this commenting style (same-line comment after to port declaration):

entity test is

port(

test0_a : std_logic; --! Port A.

test0_b : std_logic; --! Port B.

sys_clk : std_logic; --! Clock reference signal.

sys_arstn : std_logic --! Async reset signal (active_low).

);

end test;

Where am I supposed to place the @end for the @virtualbus?

None of these works:

--! @virtualbus test0

test0_a : std_logic; --! Port A.

test0_b : std_logic; --! Port B.

--! @end

--! @virtualbus test0

test0_a : std_logic; --! Port A.

test0_b : std_logic; --! Port B. @end

--! @virtualbus test0

test0_a : std_logic; --! Port A.

test0_b : std_logic; --! @end Port B.

--! @virtualbus test0

test0_a : std_logic; --! Port A.

test0_b : std_logic; --! Port B. --! @end

Neither (as also happens with the same-line comment in the example with video_out_axi_stream):

--! @virtualbus test0

test0_a : std_logic; --! Port A.

test0_b : std_logic; --! @end

fixed on v5.0.0